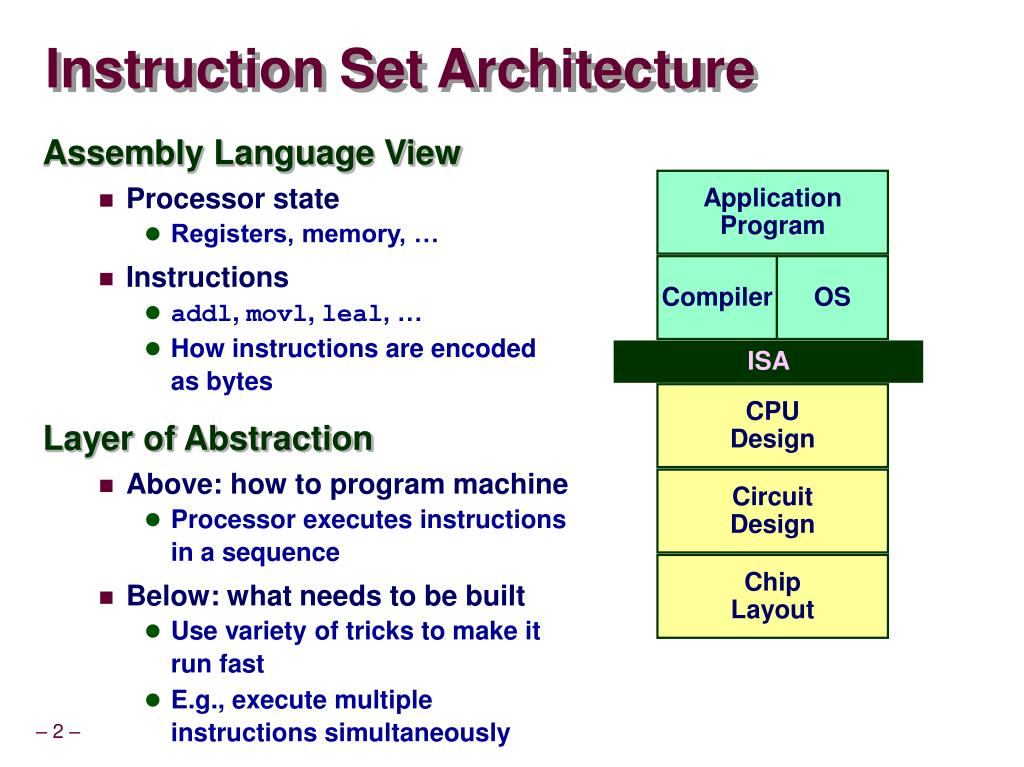

An Instruction Set Architecture (ISA) serves as the lifeblood of computing systems, defining the essential software interface for controlling a central processing unit (CPU). From early systems that lacked a cohesive ISA, today’s architectural landscape showcases a plethora of standards that enhance compatibility and portability in software applications. Over the years, the CPU architecture has dramatically evolved, with notable trends favoring prevalent models like ARM ISA for low-power devices and Intel’s x86 for desktops. As the industry witnesses a surge in new entrants, notably the open-source RISC-V, the relevance of ISAs has come to the forefront of technological discussions. Understanding the nuances of these architectures not only sparks interest among developers but also highlights the intricate relationship between ISA, microarchitecture, and overall computing performance.

At its core, the software interface that allows the central processing unit (CPU) to function is encapsulated in what we refer to as Instruction Set Architecture (ISA), a term that encompasses various computing frameworks. This foundation sets the stage for understanding the differences between various CPU designs, including RISC (Reduced Instruction Set Computer) implementations like RISC-V and established industry players such as the ARM ISA. As processors have become more sophisticated, the term ‘microarchitecture’ has emerged to describe the particulars of hardware implementation that utilize these instructions. While the ARM ISA remains dominant in mobile devices, Intel’s x86 continues to thrive in personal computing, showcasing the diverse landscape of ISA options available today. The evolution of these architectures reflects both a historical context and the continuous technological advancements shaping the future of computing.

Understanding Instruction Set Architecture (ISA)

Instruction Set Architecture (ISA) is critical in defining how software communicates with hardware, specifically the CPU. An ISA acts as an interface that ensures compatibility between the software applications developers create and the underlying hardware executing these applications. This interface encompasses various details ranging from the available commands to the methods by which these commands influence CPU behavior. In the current landscape, the evolution of ISA has been influenced significantly by the moves towards standardization which offers desirable benefits of compatibility and portability across different computer systems.

The significance of ISA cannot be understated, especially in today’s market where multiple ISAs exist such as x86, ARM, and RISC-V. Each of these architectures has unique features aimed at serving specific requirements. ARM, for instance, focuses extensively on energy efficiency while x86 aims at delivering superior performance for desktop environments. Meanwhile, RISC-V, with its open-source structure, presents an opportunity for innovation by allowing manufacturers to customize their implementations. The competitive nature of these ISAs continues to drive advancements in CPU architecture, which enhances overall performance.

The Rise of RISC-V in Modern CPU Architecture

The introduction of RISC-V as an open instruction set architecture has observed notable excitement within the tech community. RISC-V’s flexibility allows for a diverse range of implementations thereby catering to various applications, from embedded systems to high-performance computing units. The architecture is modular and can be tailored for specific use cases, offering significant cost savings, especially for companies looking to integrate advanced processing capabilities without incurring hefty licensing fees typical of proprietary ISAs. This flexibility has positioned RISC-V as an attractive option for startups and established companies alike.

However, the RISC-V architecture is not without its challenges. Its modular approach means that implementing a RISC-V CPU often involves navigating a maze of extensions and options. Unlike the rigid standards seen in ISAs like ARM, developers must validate the exact features present in their target RISC-V implementation, complicating software development significantly. Despite these hurdles, RISC-V’s adoption in various sectors, particularly within embedded computing, showcases its potential and growing recognition despite slower than anticipated uptake in performance-centric markets.

Navigating the ISA Wars: Insights into Current Competition

The ongoing competition among various instruction set architectures, often referred to as the ‘ISA Wars’, reflects the complex dynamics of computer hardware development. Historically, many manufacturers developed their own ISAs, leading to fragmentation. However, over time, a few dominant ISAs emerged, shaping the landscape of modern computing. The emergence of RISC-V further complicates this landscape as it offers a fresh alternative that challenges established players like ARM and x86, fostering an environment of innovation as companies evaluate the benefits of an open architecture.

Analyzing the competitive aspects of the ISA landscape today reveals stark divisions based on performance, application, and design philosophies. For instance, while Intel’s x86 has captured dominant market share in desktop and server-grade processors, ARM’s focus has made it the choice for mobile devices due to its efficiency. RISC-V’s introduction challenges this status quo, presenting itself as a versatile player promising customizability, though it struggles to compete on sheer performance with its more established counterparts. The ISA Wars are a testament to rapid innovation and an ever-evolving battlefield where performance, cost, and flexibility continuously collide.

The Role of Microarchitecture in ISA Performance

Microarchitecture significantly influences how well an ISA performs in practice, making it more than just a set of instructions. At the heart of this distinction lies the way CPUs are designed to execute these instructions. Modern microarchitectures implement advanced techniques like out-of-order execution, pipelining, and multi-core processing to exploit instruction-level parallelism. This indicates that two CPUs using the same ISA can exhibit vastly different performance metrics based on their microarchitectural designs, underlining the importance of the microarchitecture in achieving efficiency.

For instance, ARM’s microarchitectures have become renowned for their energy efficiency, enabling them to power devices requiring low power consumption. Conversely, x86 microarchitectures emphasize brute force performance capable of handling heavier workloads typical in server environments. In this light, the actual performance differentiators in CPUs that share the same ISA become largely the result of varying microarchitectural strategies and choices. As newer variations of ISAs such as RISC-V emerge, understanding how microarchitecture interacts with architectural design will be crucial for companies looking to optimize their products.

The Transition from x86 to ARM: A Case Study with Apple Silicon

Apple’s transition from x86 architecture to ARM with its Apple Silicon is a profound illustration of how ISA choices can influence product identity, performance, and user experience. With this move, Apple aimed to deliver improved performance and battery efficiency in its devices. The ARM architecture, particularly through its optimized microarchitecture in Apple Silicon, has seen the company reap significant rewards, allowing apps to run faster while consuming less power compared to their x86 predecessors.

The transition has also showcased the broader strategy of leveraging proprietary designs based on standardized ARM architectures to achieve a competitive edge. With the seamless integration of hardware and software within the Apple ecosystem, the results have been dramatic in terms of performance benchmarks, leaving many competitors scrambling to keep pace. This case not only reflects Apple’s shift but also highlights the larger trend toward energy-efficient computing in an era increasingly focused on sustainability.

Comparing ISAs: An Insight into RISC-V, ARM, and x86

When comparing different instruction set architectures, it becomes clear that each has its own strengths and weaknesses, making them suitable for different applications. ARM ISA, known for its power efficiency, is dominant in mobile devices, providing extended battery life without sacrificing performance. On the other hand, the x86 architecture excels in traditional computing environments such as PCs and servers where higher processing power is essential. This distinction is important for industries when selecting an architecture that aligns with their operational requirements.

RISC-V presents a new frontier that combines some of the best features of both worlds by allowing tailored implementations without the costs associated with proprietary ISAs. However, its lack of widespread adoption in high-performance environments still holds back its recognition compared to established giants. As more companies adopt RISC-V, its potential will gradually expand, enabling a more versatile computing landscape while challenging existing long-standing ISAs like ARM and x86 to innovate continuously.

Emerging Trends in ISA Development

The evolution of ISAs shows dynamic trends, influenced by technological changes and user requirements. As the demand for more efficient and powerful computational abilities grows, ISAs adapt to incorporate newer paradigms such as artificial intelligence and machine learning. These computational needs drive the development of specialized instruction sets within existing architectures or entirely new ISAs tailored for these applications. RISC-V’s openness, for example, allows for the rapid adaptation and integration of new instructions that can directly target these emerging fields, positioning it as a leader in future ISA development.

This trend of continuous evolution underscores the necessity for flexibility in CPU architecture. Companies now prioritize architectures that can adapt over time, showcasing a clear shift towards open ISAs that provide room for innovation. As industries increasingly push for advanced processing power while also conserving energy, future ISAs will likely experience enhanced collaboration and integration sessions, spurring new designs and architectures that redefine standards and drive the next generation of computing.

The Impact of Modular Designs in RISC-V

RISC-V’s modular nature represents both an opportunity and a challenge for developers. The flexibility of RISC-V allows engineers to implement a simple core for basic embedded tasks or scale up to complex designs that include various optional extensions. Each implementation may support different features, which can range widely based on the needs of the application being addressed. This modular approach encourages a vibrant ecosystem where new features can be rapidly developed and integrated, fostering innovation without the constraints commonly associated with traditional proprietary ISAs.

However, this open design also leads to potential fragmentation. Developers targeting RISC-V must ensure that the software they develop aligns with particular implementations’ capabilities. This requirement complicates the software development process compared to more rigid architectures like ARM, which have well-defined specifications for their ISAs. While RISC-V’s modular approach invites creativity and customization, it also raises challenges concerning compatibility and support, especially within environments expecting high degrees of standardization.

Future Prospects and Challenges for RISC-V

The future prospects for RISC-V appear promising yet challenging. As more companies invest in RISC-V based projects, the push for its adoption could shift industry standards, especially in sectors looking for cost-effective alternatives to proprietary ISAs. The wealth of innovation opportunities it provides potential startups and existing companies positions RISC-V as a strong player in the next generation of computing. Challenges such as the need for robust software support and kernel adaptation remain prevalent, but the ongoing community efforts may result in solutions that foster wider adoption.

The evolution of RISC-V will rely heavily on addressing community needs while ensuring that compatibility remains a priority. Market acceptance hinges on these crucial factors; therefore, collaboration among developers, ecosystem seeders, and organizations will play a pivotal role in its growth. As compounding pressures for performance and efficiency drive ongoing developments, the capabilities of RISC-V may soon highlight it as a leader amid the conventional ISAs or propel it toward a bright, strategically significant future.

Frequently Asked Questions

What is an Instruction Set Architecture (ISA)?

An Instruction Set Architecture (ISA) defines the set of instructions that a CPU can execute, establishing the software interface for interacting with hardware. It plays a crucial role in ensuring compatibility and portability across different computing systems.

How does RISC-V differ from traditional ISAs like ARM and x86?

RISC-V is a modular ISA that allows for extensive customization and addition of optional extensions, unlike traditional ISAs like ARM and x86, which have a fixed set of features. This modularity can be advantageous for embedded systems but complicates software support.

Why is the ARM ISA considered dominant in low-power device applications?

The ARM ISA is optimized for power efficiency, making it ideal for portable devices such as smartphones and tablets. Its architecture supports low-power operation while maintaining high performance, leading to widespread adoption in these applications.

What are the benefits of adopting a standard ISA for CPU architecture?

A standard ISA facilitates software development by ensuring compatibility across different hardware platforms, leading to greater portability of applications. It also helps manufacturers streamline production and reduce costs by adhering to established protocols.

How has the landscape of ISAs changed in recent years?

Recent years have seen a consolidation of ISAs as major manufacturers focus on established architectures like ARM, x86, and RISC-V. Notably, the rise of RISC-V has sparked discussions about its future impact on CPU performance and microarchitecture.

What challenges does RISC-V face in commercial applications?

RISC-V’s modular design poses challenges for software support, particularly for complex systems like Android where compatibility with various extensions must be ensured. The absence of a fixed ISA can also lead to complications in development and implementation.

What role does microarchitecture play in CPU performance?

Microarchitecture refers to the internal design of a CPU that implements an ISA, influencing factors such as speed, efficiency, and execution capabilities. Modern CPUs utilize various techniques like out-of-order execution and branch prediction to optimize performance.

How does the RISC ISA contribute to modern CPU designs?

Modern CPUs predominantly adopt RISC principles by implementing a reduced instruction set, which allows for highly optimized instruction execution. This results in better performance and easier parallel processing in contemporary computing environments.

Can you explain the significance of the OpenPOWER Foundation for ISAs?

The OpenPOWER Foundation supports the Power ISA by providing an open-source roadmap for Power architecture development. It enables innovation and collaboration in CPU architecture, allowing anyone to use the Power ISA without licensing fees.

What advantages does RISC-V offer for embedded systems?

RISC-V provides significant cost savings for embedded systems through its modularity and open-standard nature, allowing developers to customize the instruction set to meet specific application needs without the constraints of proprietary ISAs.

| Key Aspect | Description |

|---|---|

| Definition | An Instruction Set Architecture (ISA) defines the software interface for controlling a CPU. |

| Historical Context | Initially, ISAs lacked standardization, which evolved to provide compatibility and portability among CPU designs. |

| Decline of ISAs | By the 1990s, the number of mainstream ISAs decreased, with x86, ARM, and Power dominating. |

| Modern ISA Trends | Current ISAs align towards RISC principles, focusing on optimized instruction sets and features like out-of-order execution and multi-core designs. |

| RISC-V Insights | RISC-V is modular but lacks the fixed structure of other ISAs, complicating support and compatibility. |

| China’s ISA Developments | China is advancing its ISA capabilities with LoongArch and utilizing RISC-V in various applications. |

| IP Licensing | Licensing IP blocks for CPUs remains a significant factor in design and manufacturing costs. |

| Diversity in ISAs | Various ISAs offer unique advantages, leading to diverse applications and ongoing debates over their merits. |

Summary

Instruction Set Architecture (ISA) plays a crucial role in defining how CPUs operate and interact with software. As the computer landscape has evolved, multiple ISAs emerged, highlighting diverse philosophies in design and execution. While historical consolidation has led to major players like x86 and ARM dominating, newer entrants such as RISC-V offer exciting alternatives with unique structures and advantages. This ongoing evolution in ISAs emphasizes the importance of adaptability and the search for optimized solutions in computing, ensuring that as technology progresses, the diversity and relevance of various ISAs remain a topic of vital importance.